# Optoelectronic Neural Networks

K. J. Symington, J. F. Snowdon, A. J. Waddie, T. Yasue and M. R. Taghizadeh.

#### Introduction

- This presentation examines a specific application which has led to the construction of a general purpose optoelectronic neural network.

- The design and motivation for the system will be discussed.

- Results will be presented from the first generation system.

# Optoelectronic Neural Networks

- Neural networks are intractable to build to any extent on silicon.

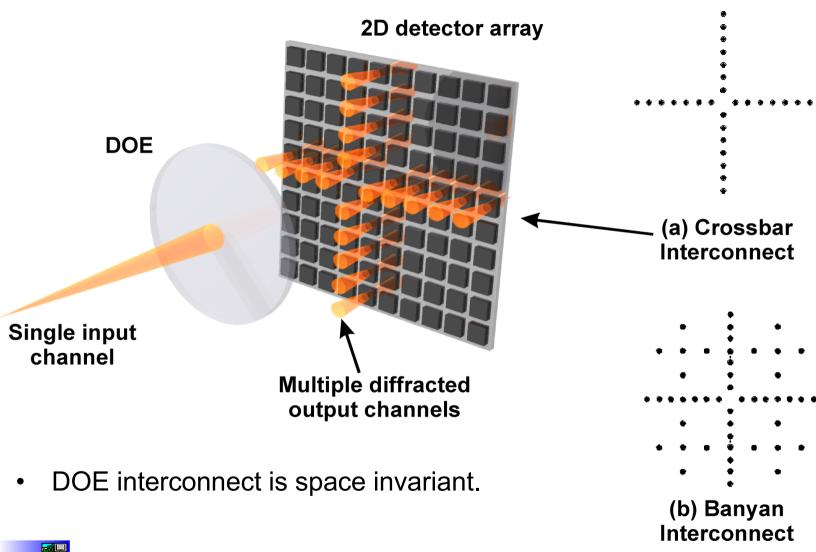

- Free-space optics can be used to perform interconnection.

- Optoelectronics allows scaleable networks.

- Input summation is also done in an inherently analogue manner.

- Noise added naturally.

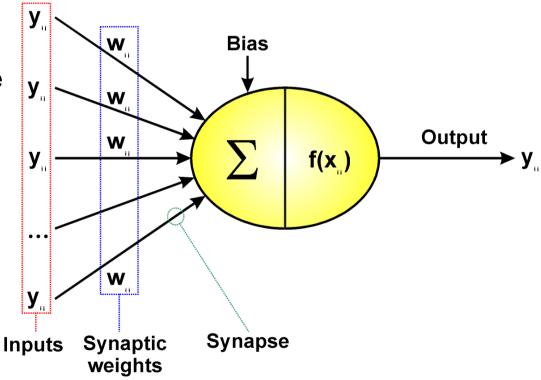

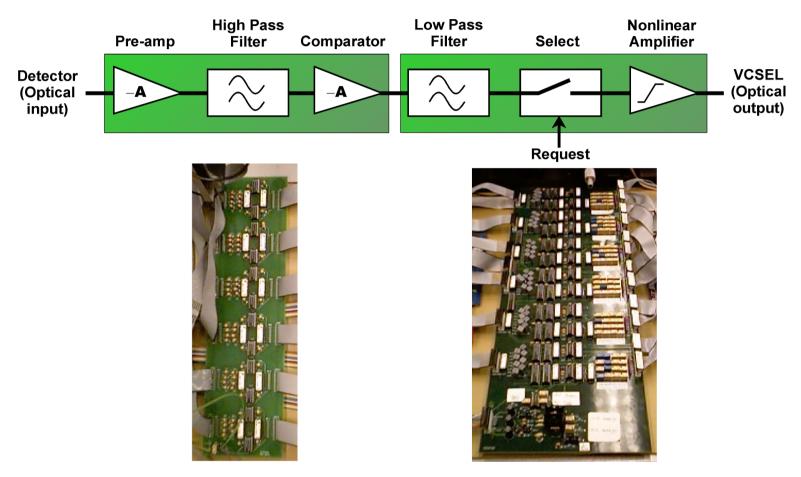

#### **Neural Processing Element (Neuron)**

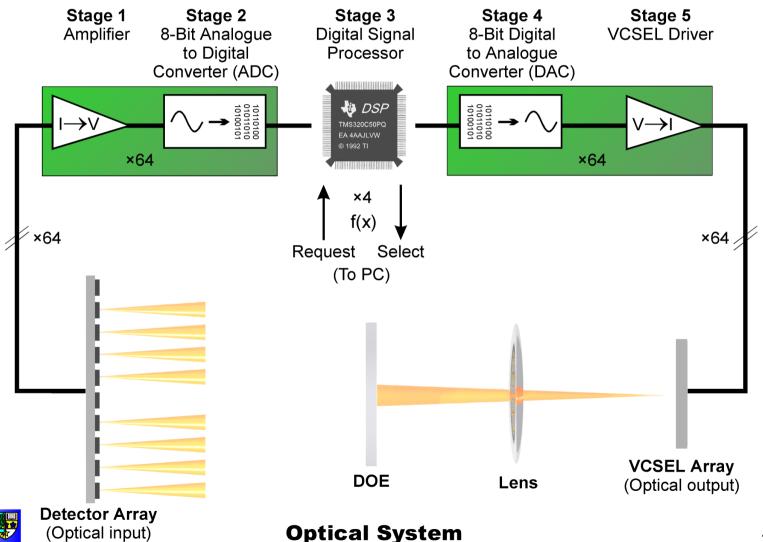

### **Current System**

#### **Electronic System**

# **Optical System**

VCSEL Array **Photodetector Array** DOE Lens

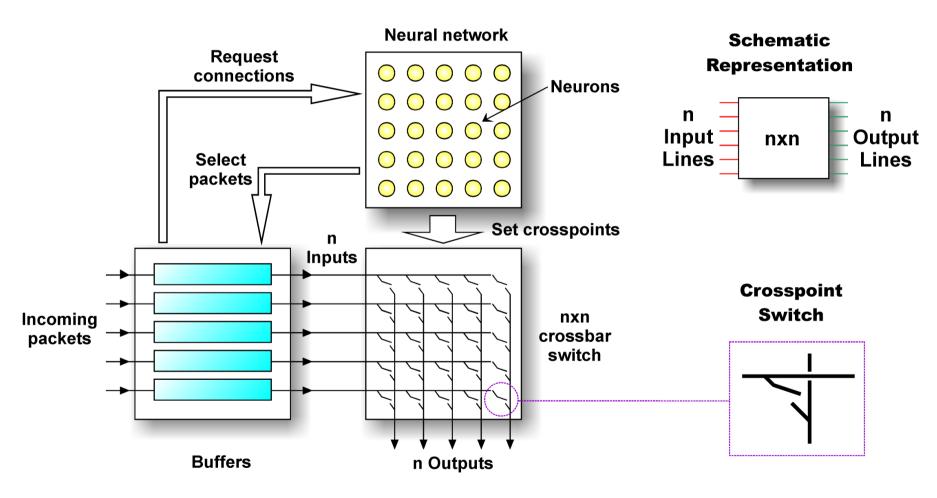

### **The Assignment Problem**

This problem can be found in situations such as:

- Network service management.

- Distributed computer systems.

- Work management systems.

- General scheduling, control or resource allocation.

Solving the assignment problem is computationally intensive.

Neural networks are capable of solving the assignment problem.

Their inherent parallelism allows them to outperform any other known method at higher orders.

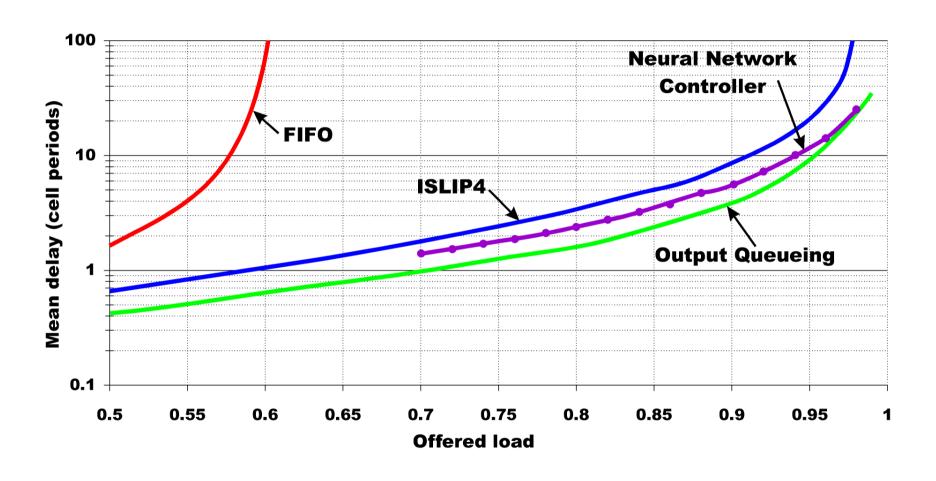

## **Crossbar Switching**

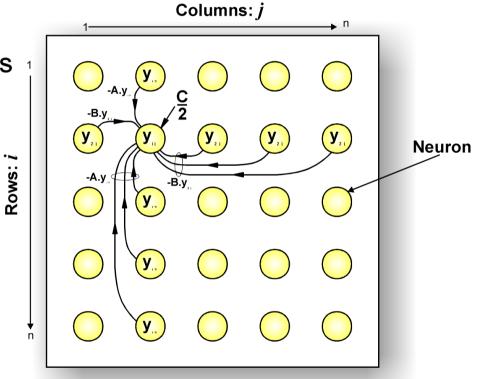

# **Algorithm**

$$x_{ij}(t) = x_{ij}(t-1) + \Delta t \left( -\alpha x_{ij} - A \sum_{k \neq j}^{n} y_{ik} - B \sum_{k \neq i}^{n} y_{kj} + \frac{C}{2} \right)$$

where:

$$Column$$

x: Summation of all the inputs to the neuron referenced by *ij*: including the bias.

y: the output of neuron ij.

A, B and C: Optimisation parameters.

**Modified Hopfield Neural Network Interconnection**

## **Optical Interconnect**

# **First Generation System**

- Constructed using discrete components.

- Lacked the ability to prioritise input packets.

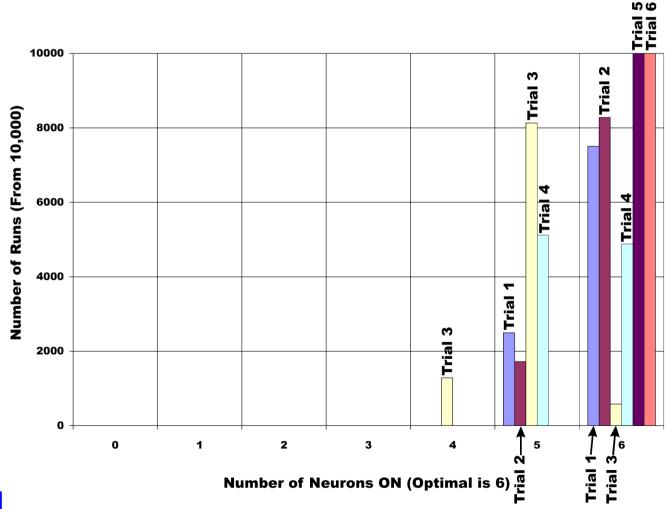

#### **Crossbar Switch Results**

Histogram of packets routed successfully in a crossbar switch.

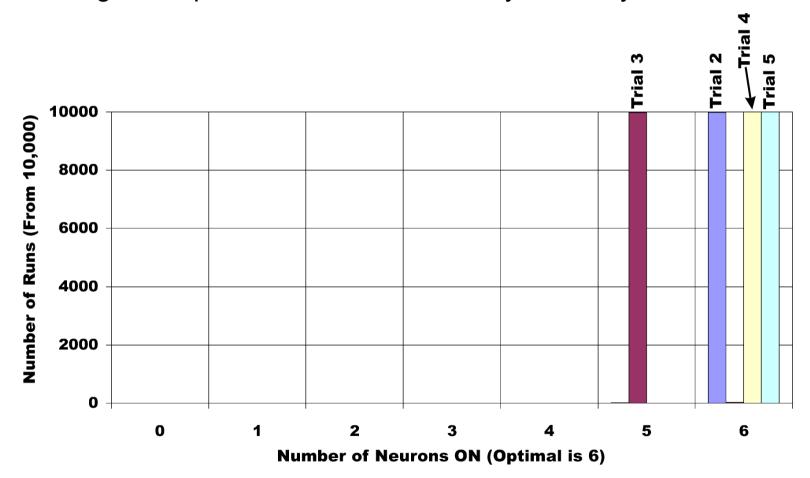

#### **Banyan Switch Results**

Histogram of packets routed successfully in a banyan switch.

#### **Performance**

#### **Conclusions**

- Second generation builds on first in that it supports prioritisation.

- Generalisation of interconnect scheme simply by replacing DOE element.

- Reconfigurability of neuron functionality by simply reprogramming DSP.

- Further work:

- Smart pixel implementation and packaging.

- FPGAs using optical interconnects.

- Novel neural algorithms and learning.